ARGONNE NATIONAL LABORATORY 9700 South Cass Avenue Argonne, IL 60439

ANL/MCS-TM-258

### Application Performance Evaluation of the HTMT Architecture<sup>\*</sup>

by

*Mark Hereld*,<sup>1,2</sup> *Ivan R. Judson*,<sup>1</sup> *Rick Stevens*<sup>1,2,3</sup> {hereld, judson, stevens}@mcs.anl.gov

<sup>1</sup>Mathematics and Computer Science Division, Argonne National Laboratory <sup>2</sup>Computation Institute, The University of Chicago <sup>3</sup>Department of Computer Science, The University of Chicago

Mathematics and Computer Science Division

Technical Memorandum No. 258

January 2003

<sup>\*</sup>Our work on the study summarized here was supported by NAS7-1260. Preparation of this report was supported by WFO Agreements with Jet Propulsion Laboratory No. 85L70 per ANL Proposal P-01014, *Hybrid Technology Multithreaded (HTMT) Application Benchmarking Final Report*, and by No. 858H3 per ANL Proposal P-97084, *Hybrid Technology Multithreaded (HTMT) Computer Architecture for Petaflops Computing*.

Argonne National Laboratory, a U. S. Department of Energy Office of Science laboratory, is operated by The University of Chicago under contract W-31-109-Eng-38.

#### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor The University of Chicago, nor any of their employees or officers, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of document authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

Available electronically at http://www.doe.gov/bridge

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from:

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831-0062 phone: (865) 576-8401 fax: (865) 576-5728 email: <u>reports@adonis.osti.gov</u>

## Contents

| Abstract                                                   |                                                                                                                                                                                                                                                                                      | 1  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1. Setting th                                              | ne Scene                                                                                                                                                                                                                                                                             | 2  |

| 1.1 Apj                                                    | plications Needing Petascale Computing                                                                                                                                                                                                                                               | 3  |

| 1.2 Roa                                                    | admap to This Report                                                                                                                                                                                                                                                                 | 5  |

| 2. HTMT Pe                                                 | rformance Evaluation Framework                                                                                                                                                                                                                                                       |    |

| 2.1 HTN                                                    | IT Overview                                                                                                                                                                                                                                                                          | 6  |

| 2.2 Guio                                                   | ling Principles                                                                                                                                                                                                                                                                      | 8  |

| 2.3 The                                                    | Modeling Hierarchy                                                                                                                                                                                                                                                                   | 9  |

| 2.3.1                                                      |                                                                                                                                                                                                                                                                                      |    |

|                                                            | Tier 2: Partitioning into Parcels                                                                                                                                                                                                                                                    |    |

|                                                            | Tier 3: Governing Equations and Parameters                                                                                                                                                                                                                                           |    |

| 2.4 Арр                                                    | lying the Model                                                                                                                                                                                                                                                                      | 13 |

| 3.1 Applic<br>3.2 Summ<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4 | Avaluation of the HTMT Architecture         ation Suite Overview.         ary of Benchmark Applications Analysis.         Dense Matrix Multiply.         Synthetic Aperture Radar.         Plasma PIC.         Volume Rendering.         mary Evaluation of Application Performance. |    |

| 4. Evaluatio                                               | on of HTMT-C as a Tool                                                                                                                                                                                                                                                               |    |

| 4.1 Key G                                                  | Questions                                                                                                                                                                                                                                                                            |    |

| 4.2 Sumn                                                   | nation of HTMT-C Remarks                                                                                                                                                                                                                                                             |    |

| 5. Final Co                                                | mments                                                                                                                                                                                                                                                                               |    |

| Acknowledg                                                 | ments                                                                                                                                                                                                                                                                                |    |

| References.                                                |                                                                                                                                                                                                                                                                                      |    |

# Application Performance Evaluation of the HTMT Architecture

by

Mark Hereld, Ivan R. Judson, and Rick Stevens

Abstract. In this report we summarize findings from a study of the predicted performance of a suite of application codes taken from the research environment and analyzed against a modeling framework for the HTMT architecture. We find that the inward bandwidth of the data vortex may be a limiting factor for some applications. We also find that available memory in the cryogenic layer is a constraining factor in the partitioning of applications into parcels. The architecture in several examples may be inadequately exploited; in particular, applications typically did not capitalize well on the available computational power or data organizational capability in the PIM layers. The application suite provided significant examples of wide excursions from the accepted (if simplified) program execution model – in particular, by required complex in-SPELL synchronization between parcels. The availability of the HTMT-C emulation environment did not contribute significantly to the ability to analyze applications, because of the large gap between the available hardware descriptions and parameters in the modeling framework and the types of data that could be collected via HTMT-C emulation runs. Detailed analysis of application performance, and indeed further credible development of the HTMT-inspired program execution model and system architecture, requires development of much better tools. Chief among them are cycle-accurate simulation tools for computational, network, and memory components. Additionally, there is a critical need for a whole system simulation tool to allow detailed programming exercises and performance tests to be developed.

We address three issues in this report:

- The landscape for applications of petaflops computing

- The performance of applications on the HTMT architecture

- The effectiveness of HTMT-C as a tool for studying and developing the HTMT architecture

We set the scene with observations about the course of application development as petaflops computing becomes possible to contemplate. We then address the topic of application performance analysis on this architecture, including our analysis framework and the concepts leading up to its adoption, summary analyses of four computationally distinct test applications, and directions in performance analysis for complex hybrid architectures such as the HTMT. We briefly discuss the strengths and weaknesses of HTMT-C, and we then conclude with comments on future performance analyses.

## **1** Setting the Scene

In the early 1990s discussions began in the United States (and perhaps elsewhere) to consider the technology paths that could lead to the development of petaflops computers – systems capable of sustaining over one quadrillion  $(10^{15})$  floating-point operations per second. The results of these discussions were well documented in a book and in a series of workshop reports (PetaFLOPS Workshop Series 1994-1999). Chief among the essential results from this work was that many applications domains could effectively use petaflops capabilities and that these applications domains have a variety of memory and turnaround requirements.

At the Pasadena Petaflops Meeting in 1994, the Bodega Bay Summer School on Petaflops in 1995, and the Petaflops II meeting in Santa Barbara in 1999, applications of petaflops systems were discussed. Applications were considered from science (including computer science), engineering, policy, national security, business, and entertainment. Requirements identified for petaflops applications included the following:

- Memory and cache footprints (the amount of memory required at each level of the memory hierarchy)

- Degree of data reuse associated with core kernels of the application, the scaling of those kernels, and the associated estimate of memory bandwidth required at each level of the memory hierarchy

- Instruction mix required by the application

- I/O requirements and secondary storage needed for intermediate results or checkpoints

- Amount of concurrency available in the application, and communications requirements (bisection bandwidth, latency, fast synchronization patterns)

- Use modality (batch, real-time, interactive, multi-user) of the application and expected turnaround times

These requirements are discussed in (Sterling, Messina, and Smith 1995). In many cases the applications analysis can be reduced to understanding the memory bandwidth requirements for kernel algorithms and the scaling properties of these core kernels (i.e., how do the memory capacity and bandwidth requirements scale as problem size increases?). Traditional scientific applications areas such as general circulation models, quantum chromodynamics, and fluid dynamics in astrophysics have relatively well understood requirements. These applications areas also have significant scalability in that the computational complexity grows faster than the memory requirements as the problem scales, implying that sustained petaflops performance could be supported by a memory system that is significantly smaller than a petabyte. Other applications areas such as data mining and decision support have a much higher need for memory. Thus, the relative importance of different types of application use modalities is an important consideration in determining feasible design points for petaflops systems. A key insight from this work is that designing breakthrough computer architectures without direct feedback from application performance analysis is a risky business at best. Consequently, the Hybrid Technology Multi-Threaded Architecture (HTMT) project included consideration of the performance of current and future application as an integral part. This report summarizes the work of the application performance study group. To execute the application performance study in concert with the rest of the HTMT design work, we assembled a group of application domain experts, sampling a wide range of disparate application types, each relying on a different set of underlying algorithms and computational needs. In addition to participating in regular all-hands HTMT progress meetings, the group convened independent workshops and working meetings to define the performance of a representative code was carried out.

# 1.1 Applications Needing Petascale Computing

Many potential applications for petaflops and petaops computing systems can be imagined (Stevens and Taylor 1995):

- Materials simulations that bridge the gap between nanoscale and macroscale (bulk materials)

- Coupled electromechanical simulations of nanoscale structures (dynamics and mechanics of micromachines)

- Full plant optimization for complex processes (chemical, manufacturing, and assembly problems)

- High-resolution reacting flow problems (combustion, chemical mixing, and multiphase flow)

- High-realism immersive virtual reality based on real-time radiosity modeling and complex scenes

- Time-dependent simulations of complex biomolecules (membranes, synthesis machinery, and DNA)

- Multidisciplinary optimization problems combining structures, fluids, and geometry

- Modeling of integrated earth systems (ocean, atmosphere, biogeosphere)

- Improved data assimilation capability applied to remote sensing and environmental models

- Computational cosmology (integration of particle models, astrophysical fluids, and radiation transport)

- Computational testing and simulation as a replacement for weapons testing (stockpile stewardship)

- Simulation of plasma fusion devices and basic physics for controlled fusion (to optimize design of future reactors)

- Design of new chemical compounds and synthesis pathways (environmental safety and cost improvements)

- Comprehensive modeling of groundwater and oil reservoirs (contamination and management)

- Modeling of complex transportation, communication, and economic systems

The potential user communities, and therefore the applications that they develop and employ, for petascale systems fall into (at least) four categories (Stevens and Taylor 1995). The first two categories represent the traditional users of high-performance computing systems. The third category captures the segment of the community that is primarily concerned with high throughput rather than capability (due either to lack of software infrastructure that scales or to the complexity of the problem solving tool chain). The fourth category represents those users that are primarily concerned with interactive analysis and rapid prototyping and could benefit dramatically from the power and storage resources of a petascale system but would need support for interaction and timesharing, both of which are not currently design goals for petaflops systems.

In the *aggressive category* we place those that have been working for some time at the frontiers of high-end computing (e.g., astrophysics, cosmology, QCD) who are extremely well prepared to move to new architectures. They have codes that are well understood from the standpoint of performance, scalability, and architectural mapping; moreover, the developers are prepared and motivated to produce new versions of these codes targeting machines several orders of magnitude increased scale.

In the *early adopters category* we place other communities that are currently using largescale machines but whose culture and code development infrastructure is less oriented toward exploiting the very latest hardware (or even experimental hardware). Applications in this category include molecular dynamics, quantum chemistry, biomolecular modeling, computational geophysics, and climate modeling. In general, these codes are slightly more complex (perhaps with more time and space scales and with more embedded physics/chemistry). The "early adopters" communities are generally ready to move to new systems; but because of the complexity of their codes and the relatively smaller size of the their groups, they generally take longer to move the substantial code base onto new systems. Because of this challenge in porting, this group has also developed software infrastructure to ease the migration to new systems (e.g., global arrays). Combined, these two categories consume the bulk of supercomputing cycles at open academic computing centers in the United States. These two groups typically form the core target for nondefense petaflops computing.

In the *high-throughput category* are user communities that have well-defined computational and data analysis problems from fields such as electronic circuit design, bioinformatics, MCAD, ECAD, design optimization, chemical engineering, and medical imaging. In many cases they lack highly scalable algorithms or even implementations that are available for ongoing development. Their systems are characterized by having well-defined interfaces to databases and other tools, and the end user/developer is often able to alter only a small portion of the overall system. This category of user can benefit from petaflops developments in several ways. First, there is the possibility of accelerating existing problems by several orders of magnitude (perhaps by enabled automated optimization) that might dramatically alter the pattern of development or problem solving. Second, the technology that enabled petaflops may also enable inexpensive teraflops for these applications, thus directly reducing the cost of these

computations. Third, petascale systems will enable components to be combined in new ways that may dramatically improve overall throughput.

The fourth category we call the *exploratory computing category*. This category includes a broad collection of users and areas where the computer is being used as a tool for rapid prototyping of ideas or algorithms or where the essential problem being solved involves interactive human-guided search. Examples here include data visualization, proof finding by automated deduction, data mining in sociology, interactive programming, and analysis using tools like Matlab and Mathematica. The key attribute of this category is that the human is in the loop and the problem-solving pattern involves a substantial amount of human interaction with the computer and with the algorithms under development. Ironically, although this category is only barely making use of existing large-scale computers, many of the future scientific and social impacts of computing are likely to come from this segment of the community. The potential benefit of petaflops/petaops computing to this category of user is immense, ranging from increasing the scale at which interactive computational experiments can be conducted to reducing the time from prototype development to widespread use. For example, if a petaflops system can be used to enable a very high level language-interpreted environment to perform at the same rate as a dedicated teraflops system, then it can be used to rapidly test ideas at full performance levels that then could be deployed on lower-cost platforms. An important element of this type of use is the capability to interactively explore terabyte or petabyte datasets that may lead to improved productivity in a number of areas. Because of the human-in-the-loop nature of this category of user, it may be feasible for multiple users to share the same petaflops systems, provided that the system can support true time-shared multi-user access. The ability to support time-shared access to petascale systems is an important new design consideration.

# 1.2 Roadmap to This Report

In Section 2 we describe the framework that we developed for evaluating the performance of applications on the hypothetical HTMT architecture. At the end of that section we describe the shortcuts we took to streamline the model to the needs and available resources of the present application study. In Sections 3 and 4 we summarize the results of our application study. We end the report with a description of extensions to the present framework that would enable a truly general class of performance analyses.

# 2 HTMT Performance Evaluation Framework

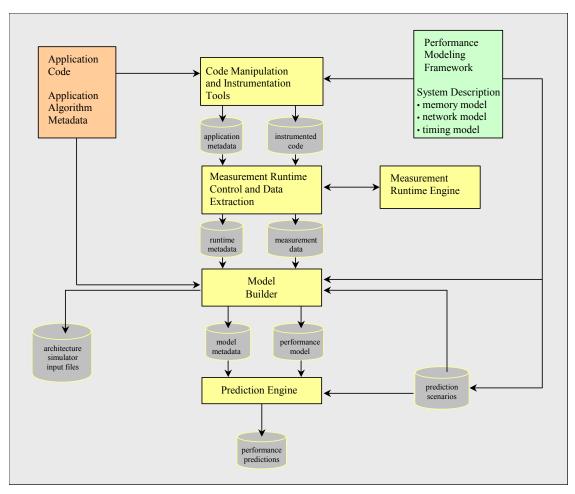

Our study began with general discussions of performance evaluation of applications on generalized abstract architectures, of which the HTMT was a particular case. At this level we considered hierarchical model descriptions, simulation techniques, emulation techniques, and possible instantiations of these using available tools (extensions to Threaded-C).

Here we describe the results of that process. In particular, we discuss the structure and organization of current and future application codes, the program execution model

developed by the HTMT research team, the parcel percolation model, and the best available parameters of the constituent hardware technologies.

The motivating questions for our study of the performance of applications on the HTMT architecture are as follows:

*Will the application perform well?* If the application does perform well, then we have effectively hidden the latency in the memory hierarchy while exploiting the aggregate performance of the system.

*What system parameters are responsible for the performance?* The answer to this question can help us determine where to apply additional effort in the hardware design. What are the key systems performance parameters? Is performance particularly sensitive to small changes in certain parameters of the hardware?

*Is the system balanced from an applications viewpoint?* Here we are looking not only for bottlenecks in the system, in the sense of the preceding question, but also for opportunities to capitalize on underutilized resources: bandwidth of the data vortex, computational power of the SPIM and DPIM layers, lateral memory bandwidth in these layers. Are these resources – memory bandwidth, communications, I/O, and compute speed – exercised (after a suitable average over applications) in a balanced way?

*Do we understand the execution model and its performance?* Apart from the performance of the hardware, we can ask whether our conception of the execution model is a source of degraded performance. Is the program execution model sufficiently expressive to enable application programmer's adequate efficient access to the hardware?

*What tools are needed to improve performance analysis and prediction?* What tools will most effectively advance our understanding of the performance of applications running the HTMT architecture beyond the limitations of the current work?

In the following section we present the modeling framework developed for this study and designed to enable us to address these questions.

# 2.1 HTMT Overview

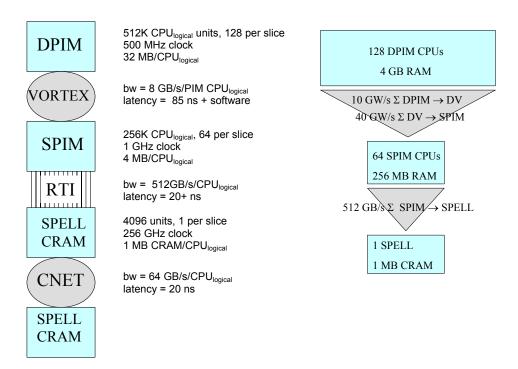

Before discussing the performance analysis framework we briefly describe the salient features of the hardware and software architecture as currently envisioned. A schematic of the central large-scale architectural features of the HTMT architecture is given in Figure 1. Depth and details can be found elsewhere regarding overall HTMT design (Sterling and Bergman, 1998), RSFQ technology (Bunyk et al. 1997; Dorojevets et al. 1999), CNET (Wittie et al. 1999), PIM (Kogge et al. 1996; Kogge 1999), VORTEX (Arend, Bergman, and Reed 1998; Arend, Reed, and Bergman 1998), and holographic memory systems (Liu, Chuang, and Psaltis 1998). The HTMT comprises several layers of

computationally enabled memory. The parameters collected in Figure 1 follow the configuration called "Oct 98" in Kogge (1999).

**Figure 1** Overview of the HTMT architecture. On the left are the major components of the system with characteristics of individual nodes and channels. On the right is a schematic of the aggregated resources at each layer of the architecture.

The fastest per node processing power is in the cryogenic SPELL layer of the architecture. Built from RSFQ logic, each SPELL runs at about 256 GHz. There are 4,096 of these in the petascale machine. The associated cryogenic memory, CRAM, is limited. Each multithreading SPELL is serviced by a cluster of room-temperature processor-in-memory nodes with associated static memory, the SPIM layer – 64 CPU nodes with 4 Mbytes each, running with 1 GHz clock, packaged 8 nodes to the chip. Communication between these layers is largely vertical. The SPIM layer is broadly connected through an optical network to the DPIM layer, a large collection of PIM nodes endowed with dynamic memory – 128 CPU nodes with 32 Mbytes each, running with a 500 MHz clock, packaged 4 nodes to the chip. For some purposes it is useful to think of vertical *slices* of the HTMT machine, each topped by a single SPELL (even though DPIMs and SPIMs can communicate freely with one another across slice "boundaries"). Each slice of the machine has one optical fiber into and out of the associated DPIM cluster. Each fiber can carry 10 Gwords/sec. The asymmetry in the data vortex port

configuration to the SPIM cluster enables bursts of 40 Gwords/sec into the SPIM, to handle the anticipated occasional higher traffic heading toward the SPELLs. Note that there are not sufficient fibers feeding the data vortex, only two for every four into the SPIM, to keep this data rate up across the entire machine – the maximum sustainable data rate from DPIM to SPIM (and vice versa) averaged over the entire machine is 10 Gwords/sec.

The program execution model, called *parcel percolation*, leverages the hardware hierarchy explicitly. Units of work in both computation and data communication are organized into parcels that contain executable code and data in proportion to their function. Parcels executed in the SPELLs (at least) are constrained by convention to be nonblocking in order to minimize the dead time of these processors. More details of the percolation model are given in the following sections. A more complete guide to the model in contained in (Gao et al. 1997; Gao et al. 1998).

# 2.2 Guiding Principles

We are guided in the design of our application framework by a few key concepts. Some have been implemented or partially implemented for the current study, while others remain as challenges for further work. As part of our remarks at the end of the paper we outline a possible automatic performance evaluation system encompassing our grandest conception of this framework.

*Models targeted at predicting runtime for applications.* The highest-level aim is to develop a framework for expressing application models that can be used to predict runtime in complex architectures such as the HTMT. The total execution time of an application running on the machine will have contributions from computation, communication, and overhead. Computation in one part of the algorithm is overlapped with communication and overhead of others. To achieve this basic goal, our models need to address data motion and computation and the costs of the HTMT execution model.

*Hierarchy of models*. Throughout the development of our framework we thought broadly about the structure of application programs, machine subsystems, architecture topology, and program execution models. We wanted to base our end-to-end performance predictions on accurate models of the pieces of the system. By working with a hierarchy of detail in our modeling strategy we hoped to capture for future use and multiple reuse the work put into characterizing the pieces. We also intend this approach as a means to enable rapid reconfiguration of the applications, machines, and execution models as part of the design cycle and optimization.

*Support for model composition.* Ultimately, our framework must support model composition in order to enable modular development of an entire model, to allow for rapid reconfiguration of a model by substitution of components for performance comparison, and to facilitate reanalysis of application performance in the face of architectural and parametric changes. We mean to include in our support of model

composition the ability to express overlapping and nonoverlapping factors and coupling between model terms.

# 2.3 The Modeling Hierarchy

We explicitly model several levels of composition: application phases, algorithm, parcels, and subsystem timing equations.

In the following paragraphs we begin, in a sense, at the highest level of the model and describe the method by which we decompose a given application into its analyzable segments. We then describe the mapping of these application fragments onto the parcel percolation model. Finally, we describe the computation of resource usage (principally processor time and communication bandwidth) and transcription of these through the higher levels of the model to the ultimate estimates of application execution time and aggregate resource usage.

## 2.3.1 Tier 1: Application Phase Decomposition

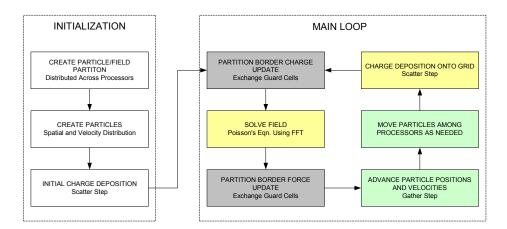

The goal of our highest-level decomposition is to divide the application into its component algorithmic phases. As an example of this breakdown, consider the plasma PIC (Norton, Decyk, and Cwik 1999) code analyzed as part of our application suite and summarized later in this report. After initialization, the code computes the evolution through time of a plasma. For each time step the algorithm can be broken down into separate phases describing the handling of different aspects of the computational physics and management of the forward propagation of the material and field configurations.

**Figure 2** Decomposition of an application into algorithm phases. In this case the PlasmaPIC algorithm passes through several discrete phases per cycle at each time step (adapted from Norton, Decyk, and Cwik 1999).

The major phases of the algorithm are (1) interpolate charge density (charge deposition) to the grid using current particle positions, (2) solve for the resulting electric field, (3)

compute the force on all particles, and (4) move the particles in response to this force. These phases are captured schematically in Figure 2.

### 2.3.2 Tier 2: Partitioning into Parcels

The next level of detail of our modeling framework bridges the algorithmic description of the application, the program execution model, and some of the aspects of the hardware architecture. At this level our model needs to address the data motion and computation explicitly. Having broken an application into its component phases and identified the principal algorithmic fragments, we now subdivide each phase into pieces consistent with the parcel percolation model (Gao et al. 1997; Gao et al. 1998) and the constraints of the architecture. This process will pave the way for expression of our model at the finest levels of detail, described in the next section.

A parcel, in this context, represents a unit of computational work, accompanied by data, (usually) requiring no additional data to run to completion. The percolation process describes the "life" of the parcel. We decompose the basic percolation of a parcel through the system into something resembling the following five phases:

- assemble gather data, attach code, build header

- dispatch administration and deposit parcel in CRAM

- execute computation in SPELL

- retire decommission and retrieve from CRAM

- scatter deliver data results

This particular decomposition does not hold faithfully in all cases, for all applications, or even for all work fragments within a given application. It is merely a guide for this level of explication. The typical associations of these parcel phases with particular layers of the computational and memory hierarchy (e.g., CRAM) are included for the sake of concreteness only. Generally, DPIM and SPIM layers of the HTMT architecture are responsible for building parcels that can be executed at the SPELL layer. DPIM has often been most closely associated with parcel assembly. Likewise, SPIM is often thought of as the executive heart of the machine – tending to the "feeding" of the SPELLs with work sufficient to keep them always busy. The SPELL most typically carries the closest association as the computational heart of the machine. The parcel percolation model underlying the HTMT execution model then suggests that parcels typically migrate, over the course of parcel assembly, from the DPIM to the SPELL. At the SPELL the parcel executes to completion; no blocking is allowed. Results are then passed back downward toward the DPIM in a scatter operation. The architecture and the program execution model are in fact more flexible than this, and the modeling framework is likewise able to express more complicated scenarios.

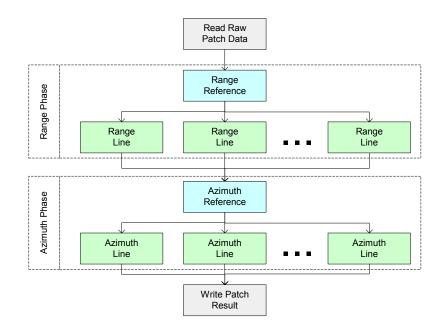

**Figure 3** Decomposition into parcels. The synthetic aperture radar (SAR) application processes patches of measurements according to the above decomposition. Patches are processed independently to create a large map. Each patch is processed in two major application phases. The phases are divided here into pieces assigned to parcels.

As an example of dividing an application further into parcels, consider the synthetic aperture radar, SAR, application analyzed in Siegel and Craymer (1999) and summarized in Section 2.3.1. Independent 2-D patches of data are analyzed in two phases, called the Range and Azimuth phases in Figure 3. For each of these phases, a single parcel computes the reference data used by a slew of parcels, each of which computes a line of the SAR reduction. The figure shows the dependencies within a patch reduction. The scattered results from the individual range line calculations are gathered "orthogonally" in the assembly of the azimuth line parcels.

#### 2.3.3 Tier 3: Governing Equations and Parameters

Each phase in the parcel's passage from assembly to deconstruction consumes hardware resources in the form of memory space, processor cycles, and communication bandwidth. It also consumes software system resources such as queue and buffer slots. In this section we present the schematic form of the equations we incorporate into our model.

We emphasize that the sums presented in these equations are only placeholders for the actual composition operations they represent. They do not explicitly represent the parallelism and pipelining that must be accounted for once the individual terms have been computed. The composition of these terms into a final estimate of the application execution time, for example, must take into account application-dependent overlapping of

work and communication terms. This composition is handled separately, and for the present it is handled manually.

We consider three components to the total execution time of a piece of computational work: the time it takes to carry out the calculation itself, the time to move data (communication), and system overhead associated with this work. When these components can be carried out entirely in parallel, the total execution time is the maximum of the three. When they must be carried out entirely serially, then the total execution time is given by the sum of the three. We represent this kind of relation generally as f().

$T_{TOTAL} = f(T_{WORK}, T_{COMMICATION}, T_{OVERHEAD}),$

and leave its final expression the circumstances dictated by the application. The same kind of function appears often in the following relations – taking on a value between the maximum of its terms and their sum depending on how much of the described work can be overlapped. Using this shorthand notation, we do not imply that the function is the *same* in all cases. It depends in detail on the interaction of the architecture, the program execution model, and the application.

Computational work can be carried out in the DPIM, SPIM, and SPELL layers of the HTMT architecture. Often, the SPELL may be used for computations and the other layers used solely to carry out operations in support of feeding the SPELLs. Borrowing the notation introduced in the previous relation, we have

$$T_{WORK} = f(W_{SPELL}, W_{SPIM}, W_{DPIM}).$$

Short of detailed microkernel timing simulations, one can characterize a kernel accounting for a simple tabulation of basic operations. By using this estimation method we are assuming that the kernel can be arranged to keep the pipeline full and free of internal contentions. Lowest-order corrections to this ideal model can be affected by adjusting the values of  $t_x$  to reflect effective time for each operation averaged over an ensemble of instructions. Accordingly, we model work done by each computing node of the architecture by breaking the kernel into contributions from computation and local or register data movement:

$$W_X = f(t_{FLOP} * N_{FLOP}, t_{IOP} * N_{IOP}, t_{LOAD} * N_{LOAD}, t_{STORE} * N_{STORE}).$$

The time to move data from one part of the architecture to another includes contributions from each of the interconnection fabric layers of the architecture:

$$T_{\text{COMMUNICATION}} = f(C_{\text{CNET}}, C_{\text{VORTEX}}, C_{\text{SPIM}}, C_{\text{DPIM}}, C_{\text{RTI}}).$$

The parameters of the model depend on the source and destination within the architecture. For example, the time to move a word from SRAM to CRAM over the RTI

is shorter than to move it from DRAM to SRAM over the Data Vortex. The constituent communications contributions are modeled with startup time, data transfer time, and account of topology in the form of hop counting. We explicitly model data motion between neighbors in the architecture and compute the end-to-end performance by suitable composition of these steps. For moves that span large lateral distances we use the algebra of hops to model the additional time required:

$C_X = t_{\text{STARTUP } X} + n * W_X + \text{DISTANCE}_X.$

This model has its shortcomings. In using it we are relying on effective values of these parameters to adequately account for many effects, including contention. We are also, for example, using full channel bandwidth as the basis for  $t_{MOVE}$ . If a single processor cannot actually fill the channel, we implicitly assume that the process has been spread across enough processors so that the data can be moved fast enough.

Finally, the overhead is broken down in our model into contributions from parcel handling, work scheduling, and algorithmic overhead. Again, the time required is bounded by the max() and sum() depending on how the component terms interact:

$T_{OVERHEAD} = f(O_{PARCEL}, O_{SCHEDULING}, O_{ALGORITHM}).$

## 2.4 Applying the Model

Having described in some detail the modeling framework that drove our application analysis, we now describe the steps taken to apply it. The scope of the task and resources available force us take aggressive measures to distill from this framework an approach that captures the essential essence, is extendible, and achieves the primary goals. Our primary goal for this study has been to aid in the design phase of the HTMT architecture. To this end we took as our highest priorities to estimate the performance of real applications as they would run on the HTMT and to identify bottlenecks in the hardware architecture and in the program execution model that would impact the HTMT design.

For each application we do the following:

- 1. Identify key phases of the main algorithms

- Distill to key phase or phases based on judgement and/or performance data from profiling

- 2. Break the key phase up into parcels

- o Identify closures

- Consider data partition size vs. available memory (CRAM)

- 3. Develop a functional form capturing complexity of each phase

- Measure or derive complexity coefficients for each term in the model

- Fit parameters to simulation data (machine model and applications model terms)

- 4. Evaluate the model components by hand, using spreadsheets, etc.

- Compute time cost for each basic resource

- Normalize to use entire slice (for example all DPIMs)

- 5. Compose models for end-to-end prediction

- Compute resource utilization to identify bottlenecks in the architecture

- o Assess impact on available memory at all layers

- Calculate pipeline timing for critical parcels

**Table 1** Summary of parameters describing the basic HTMT subsystem performance and the configuration of the entire system. (\* For the steady-state calculations of this study, we cannot take advantage of this factor of 4 because there is only one fiber from the DPIM layer to feed the SPIM.)

|                                    | В         | asic Paramete            | rs of the Model |                         |                |

|------------------------------------|-----------|--------------------------|-----------------|-------------------------|----------------|

|                                    |           | Available<br>Parallelism | Aggregate       | Aggregate<br>HTMT Value |                |

| Parameter                          | Value     | per Slice                | Slice Value     | (4096 Slices)           | Units          |

| Work                               |           |                          |                 |                         |                |

| T <sub>SPELL</sub> <sup>-1</sup>   | 2.56 E+11 | 1                        | 1 2.56 E+1      | 1 1.05 E+1              | 5 [cycles/sec] |

| T <sub>SPIM</sub> <sup>-1</sup>    | 1.00 E+09 | 64                       | 4 6.40 E+1      | 0 2.62 E+1              | 4 [cycles/sec] |

| T <sub>DPIM</sub> <sup>-1</sup>    | 5.00 E+08 | 128                      | 6.40 E+1        | 0 2.62 E+1              | 4 [cycles/sec] |

| Communication                      |           |                          |                 |                         |                |

| $T_{S to C}^{-1}$                  | 6.41 E+10 | ) 1                      | 1 6.41 E+1      | 0 2.63 E+1              | 4 [W/sec]      |

| $T_{C to S}^{-1}$                  | 6.41 E+10 | ) 1                      | 1 6.41 E+1      | 0 2.63 E+1              | 4 [W/sec]      |

| T <sub>DV to S</sub> <sup>-1</sup> | 1.00 E+10 | 4'                       | * 4.00 E+1      | 0 1.64 E+1              | 4 [W/sec]      |

| T <sub>S to DV</sub> <sup>-1</sup> | 1.00 E+10 | ) 1                      | 1 1.00 E+1      | 0 4.10 E+1              | 3 [W/sec]      |

| T <sub>D to DV</sub> <sup>-1</sup> | 1.00 E+10 | ) 1                      | 1 1.00 E+1      | 0 4.10 E+1              | 3 [W/sec]      |

| T <sub>DV to D</sub> <sup>-1</sup> | 1.00 E+10 | ) 1                      | 1 1.00 E+1      | 0 4.10 E+1              | 3 [W/sec]      |

| T <sub>H to D</sub> <sup>-1</sup>  | 5.00 E+10 | ) 1                      | 1 5.00 E+1      | 0 2.05 E+1              | 4 [W/sec]      |

| T <sub>D to H</sub> <sup>-1</sup>  | 1.25 E+09 | ) 1                      | 1 1.25 E+0      | 9 5.12 E+1              | 2 [W/sec]      |

| Memory                             |           |                          |                 |                         |                |

| M <sub>CRAM</sub>                  | 1.31 E+05 | ; 1                      | 1 1.31 E+0      | 5 5.37 E+0              | 8 [W]          |

| M <sub>SRAM</sub>                  | 5.24 E+05 | 64                       | 4 3.36 E+0      | 7 1.37 E+1              | 1 [W]          |

| M <sub>DRAM</sub>                  | 4.19 E+06 | 128                      | 5.37 E+0        | 8 2.20 E+1              | 2 [W]          |

| M <sub>HRAM</sub>                  | 1.00 E+09 | 32                       | 2 3.20 E+1      | 0 1.31 E+1              | 4 [W]          |

Table 1 summarizes some of the parameters that drive our model. The per element values are in the second column – scaled, for example, to the single logical computing element or the data vortex optical fiber. The number of elements is given under the heading *Available Parallelism* and is used to compute the aggregate value available per slice. In the penultimate column the parameters are scaled to aggregate the resource over the entire 4096-slice HTMT machine. Units are given in the final column. Note that the memory capacity is given here in words whereas in Figure 1 it is given in bytes.

## 3 Critical Evaluation of the HTMT Architecture

In this section we summarize the results of our evaluation of the HTMT design.

# 3.1 Application Suite Overview

We considered in detail a fairly large number of applications as part of our survey for this analysis:

- adaptive N-body problem algorithm

- plasma particle-in-cell code

- Cannon's algorithm for matrix multiplication

- volume rendering

- synthetic aperture radar

- molecular dynamics

We attempted to sample the space of application domains broadly in an effort to find examples for our test suite that would stress the architecture differently and with different data access patterns. The applications finally chosen for inclusion in this report were those analyzed in the greatest detail. In the following section we summarize the results from the individual applications: a dense matrix multiplication kernel, synthetic aperture radar, plasma PIC, and volume rendering.

# 3.2 Summary of Benchmark Applications Analysis

In this section we present a summary of each analysis, including a brief description of the application, its principal computational elements, a snapshot of its equilibrium resource utilization, and an estimate of the largest job size that will run on the petascale HTMT.

## 3.2.1 Dense Matrix Multiply

Matrix multiplication plays a key role in many applications, and so we are interested in whether it poses any particular problems for the HTMT architecture and program execution model. Following is a brief summary of the analysis of an implementation of Cannon's algorithm for dense matrix multiplication reported by Amaral et al. (1999). In the basic algorithm, two large matrices (call them A and B) to be multiplied (giving C) are first partitioned into  $t^2$  blocks each. Each of the matrices is M by M, where M = t \* s \* $b_c$ . The final result requires calculating the products of blocks from A with blocks from B. Cannon's algorithm is used to compute this intermediate result, the product of two blocks, wherein each is partitioned into  $s^2$  subblocks (each  $b_c$  by  $b_c$  elements in size) and distributed among  $s^2$  processing elements (the SPELLs) in a special initial pattern. The processors are imagined to be arranged in an s by s grid with toroidally wrapped communication paths. The algorithm prescribes a data exchange pattern wherein the subblocks from A are moved to the left on the grid and the subblocks from B are moved up between subblock multiplications. At the end of s iterations, each processor has accumulated a subblock of the final result for the current block multiplication. For each subblock of C to be computed, t of these A and B subblocks are multiplied and accumulated. By the end, this kernel operation, the subblock multiplication, is performed  $t^3$  times to compute the final  $t^2$  blocks of C.

The  $b_c$  by  $b_c$  element subblocks are limited in size by available CRAM. The value of  $s^2$  is chosen to match the total number of SPELLs available, 4096 for the full HTMT design. And the value of  $t^2$  is set by the requirement that 3 bundles of  $t^2$  subblocks fit in SRAM. This sets the natural limit to the size, M, of the matrix that can be multiplied with this method. As Amaral et al. (1999) point out, the algorithm can be scaled to larger matrices by breaking them down into this natural size.

This application fragment differs from the others analysed in that it introduces substantial interparcel communication between SPELLs over the CNET. The data exchange step described above is carried out over the CNET. Unlike the other applications, the  $s^2$  SPELLs are all running threads that are synchronized without communicating to the SPIMs for the *s* iterations required to compute the block product.

Also interesting, in this implementation the t subblock multiplications needed for a single C subblock are accumulated in the CRAM, meaning that there is a further unusual dependency: t generations of subblock pairs must be percolated into the CRAM sequentially while code and data remain *live*. The parcels sent to the SPELL in this application are not nonblocking. The execution time was estimated to be

$T = D_t[A] + D_t[B] + 2*IP_{DS} + t^2 * T_B + OP_{SD} + D_t[C]$  $T_B = t * s * M_S + (2t + 1) * IP_{SC}.$

The first equation describes the general structure of the calculation. The  $D_t[$ ] terms represent the transformation on the matrices that must be performed to optimally match them to the streaming communication pattern of the actual multiplication. These are nonoverlapping transformations carried out by the DPIMs. The third and fifth terms represent the percolation of the data between DPIM and SPIM. And the fourth term describes the  $t^2$  block sets that must be injected into the CRAM and multiplied by the SPELLs. The details of that process are shown in the second equation, including the cost of the multiplication and the communication terms, in that order. The parameter descriptions and their estimated values are collected in Table 2. The total time for data transformation, done in the DPIMs, is 2.68 seconds. The total time spent multiplying subblocks in the SPELLs, given by  $t^3 * s * M_S$ , is 13.2 seconds. The remaining total time figures for different portions of the execution are in the last column of Table 3.

The results from the analysis of the model are organized into parcels in Table 3. Before the matrices can be efficiently broken into parcels for the multiplication described above, they must undergo a transformation. This is estimated to take 1.33 seconds for each matrix. With both *A* and *B* transformed, we then begin moving a coordinated stream of subblock parcels up to the SPELLs to be multiplied. The *Bundle Up* parcel requires 13.2  $\mu$ sec to move subblocks for both of the multipliers; this operation is performed in parallel across the entire machine to install all of the subblocks (two per SPELL) needed to compute the product of a full block. For each of these, the *Block Multiply* parcel iterates *s* times on subblock multiplications (costing 11.7  $\mu$ sec each) interleaved with CNET-mediated subblock exchanges (costing 0.94  $\mu$ sec each). At the end of this 808  $\mu$ sec the

result is sent back down to the DPIM (*Bundle Down*) to be transformed into normal order.

| A data transform in DRAM                          | $D_t[A]$         | 1.37 G cycles | 1.33 seconds      |

|---------------------------------------------------|------------------|---------------|-------------------|

| B data transform in DRAM                          | $D_t[B]$         | 1.37 G cycles | 1.33 seconds      |

|                                                   |                  |               |                   |

| C data transform in DRAM                          | $D_t[C]$         | 21.1 M cycles | 20.5 E-03 seconds |

| Percolation of block D -> S RAM                   | IP <sub>DS</sub> | 10.6 M W      | 10.3 E-03 seconds |

| Percolation of subblock S->C RAM                  | IP <sub>SC</sub> | 15.6 K W      | 6.6 E-06 seconds  |

| Subblock multiply                                 | Ms               | 250. M cycles | 11.7 E-06 seconds |

| Subblock exchange among SPELLs                    | Ds               | W             | 0.94 E-06 seconds |

| Percolation of C subblock C->S RAM                | OP <sub>CS</sub> | 15.6 K W      | 6.6 E-06 seconds  |

| Percolation of C block S->D RAM                   | OP <sub>SD</sub> | 10.6 M W      | 10.3 E-03 seconds |

| Matrix partition factor (t <sup>2</sup> blocks)   | t                |               | 26                |

| Block partition factor (s <sup>2</sup> subblocks) | S                |               | 64                |

| Subblock dimension                                | b <sub>c</sub>   |               | 125               |

| Matrix dimension ( = t * s * $b_c$ )              | М                |               | 208000            |

Table 2

Parameters and calculated values for the Cannon algorithm dense matrix multiplication.

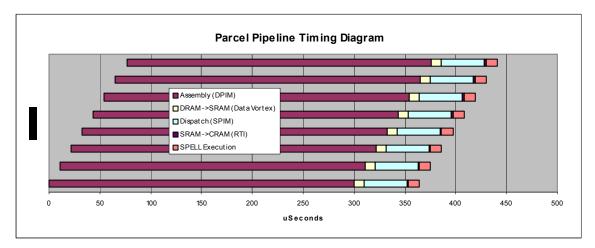

The utilization numbers in the second half of Table 3 are normalized to the principal resource used by each parcel. For example, the *Block Multiply* parcel takes 750  $\mu$ sec of SPELL execution time. Percolation of the parcel from SRAM to CRAM takes 13.2  $\mu$ sec, or 1.8 % of the SPELL execution time. The resources are normalized in this way on a parcel-by-parcel basis. This view tells us the how resource use is balanced within a parcel. When weighted by the total execution time of the parcel and the number of times it is repeated, it tells us how system resources are distributed among the ensemble of parcels. Finally, it gives us a quick way to see how the parcels will pipeline.

The *Block Multiply* parcels require 13.2 seconds to execute (product of parcel time and parcel reps) and dominates the overall execution of the algorithm. Both CRAM and DRAM are well used. The only other resource that sees significant use is the DPIM execution of the matrix *Transform* parcels, contributing a total of 2.7 seconds, which does not overlap with the *Block Multiply*. DRAM is not heavily subscribed, leading to the possibility of performing several matrix multiplications in pipelined fashion, overlapping the transformation of one with the block multiplies of another to approach 100% utilization of the SPELL.

**Table 3** Parcel summary for the Cannon algorithm. The top half of the table gives the fundamental resources required for each parcel in terms of processor cycles, words to be moved, and words of storage. The bottom half restates these resources in terms of the parameters of the architecture to give execution time and communication time. (An entire subblock is percolated out of the CRAM only after t=26 executions of the parcel have accumulated the result – the value here is the entire subblock amortized over the t=26 executions of the basic block multiply.)

| Parcel<br>Summary        |                  | Transform<br>A | Transform<br>B | Bundle<br>Up | Block<br>Multiply | Bundle<br>Down | Transfor<br>m C |                    |

|--------------------------|------------------|----------------|----------------|--------------|-------------------|----------------|-----------------|--------------------|

| Parcel Time              |                  | 1.33 s         | 1.33 s         | 21. ms       | 750 μs            | 10.5 ms        | 20.5 ms         | Seconds            |

| Parcel Reps              |                  | 1              | 1              | 1            | 17.6 K            | 1              | 1               | Reps               |

| Processor                | SPELL            |                |                |              | 250. M            |                |                 | Cycles             |

|                          | SPIM             | 4.07.0         | 4.07.0         | _            |                   |                | 04.4.14         | Cycles             |

| Communication            | DPIM<br>S => C   | 1.37 G         | 1.37 G         |              | 15.6 K            |                | 21.1 M          | Cycles<br>W        |

| Communication            | S <= C           |                |                |              | 600*              |                |                 | Ŵ                  |

|                          | S => S           |                |                |              |                   |                |                 | W                  |

|                          | D => S<br>D <= S |                |                | 21.1 M       |                   | 10.6 M         |                 | W                  |

|                          | D <= 3<br>D => D |                |                | _            |                   | 10.6 10        |                 | W                  |

|                          | H => D           |                |                |              |                   |                |                 | W                  |

|                          | H <= D           |                |                |              |                   |                |                 | W                  |

| Memory                   | CRAM<br>SRAM     |                |                | 125. K       | 65.5 K            | 125. K         |                 | W                  |

|                          | DRAM             | 14.1 M         | 14.1 M         | 125. K       |                   | 12J. K         | 14.1 M          | Ŵ                  |

|                          | HRAM             |                |                |              |                   |                |                 | W                  |

| Processor                |                  |                |                |              |                   |                |                 |                    |

| Utilization              | SPELL            |                |                |              | 100 %             |                |                 | 13.2 s             |

|                          | SPIM             |                |                |              |                   |                |                 |                    |

| Developiette             | DPIM             | 100 %          | 100 %          |              |                   |                | 100 %           | 2.7 s              |

| Bandwidth<br>Utilization | S => C           |                |                |              | 1.8 %             |                |                 | 0.230 s            |

| Otilization              | S <= C           |                |                |              | 0.03 %            |                |                 | 0.004 s            |

|                          | S => S           |                |                |              | _                 |                | _               |                    |

|                          | D => S<br>D <= S |                |                | 100 %        |                   | 100 %          |                 | 0.021 s<br>0.010 s |

|                          | D <= 3<br>D => D |                |                | _            |                   | 100 %          |                 | 0.010 \$           |

|                          | H => D           |                |                | -            |                   |                |                 |                    |

|                          | H <= D           |                |                |              |                   |                |                 |                    |

| Memory<br>Utilization    | CRAM             |                |                |              | 49%               |                |                 |                    |

|                          | SRAM             | -              | -              | 99 %         | +370              | 99 %           | _               |                    |

|                          | DRAM             | 2.8%           | 2.8%           |              |                   |                | 2.8%            |                    |

|                          | HRAM             |                |                |              |                   |                |                 | J                  |

### 3.2.2 Synthetic Aperture Radar

The results presented here are derived from the analysis and report by Siegel and Craymer (1999). With a technique known as synthetic aperture radar (SAR), Earth orbiting radar instrumentation can be processed to extract extremely detailed relief

images of the Earth's surface using wavelengths that are relatively insensitive to water vapor in the atmosphere. Furthermore, because phase information is maintained at these relatively long wavelengths, images from successive orbits can be combined to form difference images sufficiently accurate to shed light on the effects of seismic activity. The return signal from a transmitted chirp is analyzed in the SAR algorithm/

### 3.2.2.1 Performance Analysis of SAR on HTMT

The algorithm proceeds in the following general way. The basic unit of work in the SAR calculation is processing a patch of data, a series of 1-D return signals each contributing a line to the 2-D patch. The patch computation is decomposed into two phases called range focusing and azimuth focusing. The phases are quite similar in general construction, beginning with per patch initialization computations followed by serial processing of lines.

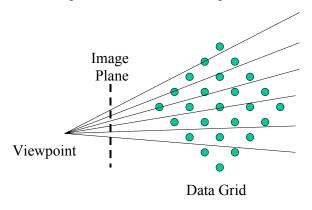

Figure 3, presented above in Section 2.3.2, sketches the key features of the algorithm in terms of its decomposition into phases and parcels. Salient facts include the following. Reductions of data from separate patches are independent and are carried out in parallel. Range line computations within a patch can be carried out in parallel. Azimuth line computations for a given patch cannot begin until all of the range line computations have completed. Parcels are assembled by the DPIM in the DRAM. A typical patch is 11,812 x 4096 points.

The SAR calculation comprises six basic parcels (Figure 3): one to stage raw patch data from HRAM into DRAM, two each for each of the two phases of the computation, and one that posts the resulting patch image to HRAM. There is one instance of the range reference parcel for each 11,812 instances of a range line parcel. These are followed by one instance of the azimuth reference parcel and 4096 instances of the azimuth line parcel. Other miscellaneous parts of the computation are neglected in this analysis.

A few notes about the model:

- 1. If the SPELL computation takes a lot of time compared with communication and computational work at lower levels, then the system overhead will probably not be critical in our model. In particular, the model doesn't use many SPIM cycles explicitly, so we relegate the SPIM layer to a "pass through" role and ignore it.

- 2. In this application the Range Reference parcel provides data that is needed by each of the Range Line parcels. The reference data is left in CRAM while Range Line parcels are fed to the SPELL to use it. In some sense the Range Reference parcel has been dispatched to the SPELL without its closure (i.e., the rest of the Range Line data).

- 3. The table lookup and conversion of raw bytes into complex numbers are currently modeled as part of the Read Patch operation. The process could be done on a line-by-line basis as part of the line parcel work to greatly decrease the time to gather data as the raw data is 16 times smaller than the formatted data.

Execution time is modeled by a combination of two terms for computation in the SPELL and one term for work done in the DPIM. Table 4 gives the model coefficients for the computational work done in each parcel type. As an example, the time spent executing a Range Line parcel in the SPELL is modeled as

$$T_{\text{EXECUTE}} = T_{\text{SPELL}} * (6 * N_{\text{RANGE}} + 10 * N_{\text{RANGE}} ' * \log_2(N_{\text{RANGE}} ')).$$

**Table 4** Shorthand for the models describing principal compute cycles for each of the SAR parcel types. *Nr* and *Na* are the number of elements in the range and azimuth directions, respectively. *Ni* represents one of these, depending on context. The primed quantities in the log term indicate that the number, *Ni*, must be padded to the next highest power of two.

| SAR Execution<br>Coefficients | Read<br>Patch | Range<br>Reference | Range<br>Line | Azimuth<br>Reference | Azimuth<br>Line | Write<br>Results |

|-------------------------------|---------------|--------------------|---------------|----------------------|-----------------|------------------|

| SPELL                         |               |                    |               |                      |                 |                  |

| Ni                            |               | 22                 | 6             | 28                   | 6               |                  |

| Ni' * log <sub>2</sub> (Ni')  |               | 5                  | 10            | 5                    | 10              |                  |

| DPIM                          |               |                    |               |                      |                 |                  |

| Nr * Na                       | 10            |                    |               |                      |                 | 10               |

The time required to assemble, gather, execute, scatter, and dispense each of the six parcel types is computed along similar lines. Table 5 summarizes these estimates in a way intended to highlight bottlenecks and overall distribution of resources. For each parcel type the time required to carry out the execution phase of its progress through the percolation is listed in the first line. In the case of the Range Line parcel, this is the time it spends in the SPELL. The total time for a single SPELL to calculate a patch of 4096 range lines and 11,812 azimuth lines is approximately 62 msec, giving an execution rate of 66,000 patches per second for a 4096-slice HTMT system.

The remaining rows show the resource utilization. The computing utilization, typically in the SPELL, is defined as 100%. The communication utilization factors are expressed as the fraction of the available communication bandwidth used to deliver the data in the time it takes to execute the parcel in the SPELL. Anything below 100% is interpreted as meaning there is bandwidth to spare. The memory used is expressed as a fraction of the memory available.

What is the largest dataset we can process in this way? CRAM utilization is determined by the need to keep at least one thread running, another ready to run, and the always resident data computed in the *reference* parcel – *Range Line* parcels dominate the computation. Siegel and Craymer calculate that each 11812 x 4096 point patch of input data requires 92 MB of storage (2 bytes per data value). If half of the available HRAM is used to hold input data, then the scale of our job is set at 5.4 million raw patches; we will use 50% utilization of the HRAM in our summary in Table 5. At 66,000 patches per second, it will take 82 seconds to reduce this stash of patches, which represents a rate into the DPIM of raw patch date of 5.8 TB/sec. Table 5 shows that the flow of data to the SPELLs for processing can be sustained by using very little of the available SRAM, DRAM, and HRAM. This reassures us that the data can be staged out of HRAM as needed.

**Table 5** Summary of the execution time and relative resource utilization factors for each of the six parcels that make up the basic SAR application.

| PARCEL                |                  | READ    | RANGE     | RANGE        | AZIMUTH   | AZIMUTH      | WRITE   | Ī                |

|-----------------------|------------------|---------|-----------|--------------|-----------|--------------|---------|------------------|

| SUMMARY               |                  | PATCH   | REFERENCE | LINE         | REFERENCE | LINE         | PATCH   |                  |

| Parcel Execution      |                  | 1900 μs | 5.5 μs    | 9.3 μs       | 1.4 μs    | 2.0 μs       | 1900 μs |                  |

| Repetitions           |                  | 1900 μ5 | 5.5 μ5    | 9.5 μ5       | 1.4 μ5    | 2.0 μ5       | 1900 μ5 |                  |

| per Patch             |                  | 1       | 1         | 4096         | 1         | 11812        | 1       |                  |

|                       |                  |         |           |              |           |              |         |                  |

| Processor             |                  |         |           |              |           |              |         |                  |

| Work                  | SPELL            |         | 1.41 M    | 2.39 M       | 360 K     | 516 K        |         | Cycles           |

|                       | SPIM<br>DPIM     | 484 M   |           |              |           |              | 484 M   | Cycles<br>Cycles |

| Communication         |                  | -10-111 |           |              |           |              | -10-111 | Cycles           |

| Load                  | S => C           |         | 32.8 K    | 32.8 K       | 8.2 K     | 8.2 K        |         | W                |

|                       | S <= C           |         |           | 32.8 K       |           | 8.2 K        |         | W                |

|                       | S => S<br>D => S |         | 23.6 K    | 23.6 K       | 8.2 K     | 8.2 K        |         | W<br>W           |

|                       | D <= S           |         | 23.0 K    | 32.8 K       | 0.2 K     | 8.2 K        |         | Ŵ                |

|                       | D => D           |         |           |              |           |              |         | W                |

|                       | H => D           | 48 M    |           |              |           |              | 48 M    | W                |

| Memory                | H <= D           |         |           |              |           |              |         | W                |

| Requirements          | CRAM             |         | 524 K     | 262 K        | 131 K     | 66 K         |         | в                |

|                       | SRAM             | _       | 189 K     | 189 K        | 66 K      | 66 K         |         | В                |

|                       | DRAM             | 774 M   | 189 K     | 189 K        | 66 K      | 66 K         | 774 M   | В                |

|                       | HRAM             | 96 M    |           |              |           |              | 96 M    | В                |

| Processor             |                  |         |           |              |           |              |         |                  |

| Utilization           | SPELL            |         | 100 %     | 100 %        | 100 %     | 100 %        |         |                  |

|                       | SPIM             | 100.0/  |           |              |           |              | 100.0/  |                  |

| Bandwidth             | DPIM             | 100 %   |           |              |           |              | 100 %   |                  |

| Utilization           | S => C           |         | 9.3 %     | 5.5 %        | 9.1 %     | 6.3 %        |         |                  |

|                       | S <= C           |         |           | 5.5 %        |           | 6.3 %        |         |                  |

|                       | S => S           |         | 10.0/     | 05.0(        | 50.0/     | 4.4.0/       |         |                  |

|                       | D => S<br>D <= S |         | 43 %      | 25 %<br>35 % | 58 %      | 41 %<br>41 % |         |                  |

|                       | D <= 3<br>D => D |         |           | 55 /6        |           | 41 /0        |         |                  |

|                       | H => D           | 51 %    |           |              |           |              |         |                  |

|                       | H <= D           |         |           |              |           |              | 51 %    |                  |

| Memory<br>Utilization | CRAM             |         | 51 %      | 26 %         | 13 %      | 6.4 %        |         |                  |

| Guilzation            | SRAM             |         | .07 %     | .07 %        | .03 %     | .03 %        |         |                  |

|                       | DRAM             | 19 %    | .005 %    | .005 %       | .002 %    | .002 %       | 19 %    |                  |

|                       | HRAM             | .04 %   |           |              |           |              | .04 %   |                  |

## 3.2.3 Plasma PIC

The plasma PIC code simulates the interaction of millions of charged particles with the electromagnetic field that they produce. It is an example of a code that is used to understand the behavior of a plasma such as that generated by proposed fusion reactors. The analysis described here is paraphrased from Norton, Decyk, and Cwik (1999).

#### 3.2.3.1 Classical MPP Algorithm for Plasma PIC

Figure 2, shown in Section 2.3.1, depicts the general steps in the plasma PIC algorithm as implemented for a distributed-memory machine. The application loop alternates between computing fields based on current charged particle positions (and velocities) and advancing the positions (and velocities) of these particles under the force of this field. These can be thought of as the two principal phases in the application. Between these two phases the problem data is repartitioned to improve the efficiency of each. The repartitioning is accomplished by data exchange, called guard cell exchange in the figure, between the processors of the MPP implementation.

Particle push, as the position (and velocity) update calculation is called, is the most computationally expensive phase of the algorithm. The analysis focuses on this phase.

For each processor in the MPP implementation, the problem is laid out on a grid of  $(N_G+1)^3$  field points, with an associated field  $(E_X, E_Y, E_Z)$  at each point. These grid points partition the volume into  $(N_G+1)^3$  cells with an average of  $N_P$  particles per cell. The memory required is  $(3 + 6 * N_P) * N_G^3$  words per processor.

By using a quadratic interpolation of the electrostatic field, the approximate number of operations is extracted from an existing implementation and found to be 200 floating-point operations per particle. The model discussed here accounts for additional work in the form of integer operations, loads, and stores, by adjusting this figure by an empirically determined floating-point utilization factor of 88% to correct for the instruction mix. Hence the net time to carry out the particle push for a single particle is taken to be (200 \*  $t_{FLOAT} / .88$ ).

#### 3.2.3.2 Performance Analysis of Plasma PIC on HTMT

Analysis of the performance of the plasma PIC code on the HTMT begins by mapping the computation of the particle push onto the SPELL and accounting for the data motion through the memory hierarchy. The values of  $N_G$  and  $N_P$  are tuned to fit CRAM. If we use the typical value of  $N_P = 16$ ,  $N_G$  becomes 10, for a parcel size of 100K words. We first consider a single slice of the HTMT architecture, topped by a single SPELL cryogenic processor.

|                              |          |        |           | A           |             |

|------------------------------|----------|--------|-----------|-------------|-------------|

|                              |          |        |           | Available   |             |

| Parcel                       |          |        |           | Parallelism |             |

| Phase                        | Quantity |        | Time      | per Slice   | Utilization |